La Memoria Cache.

Principio di funzionamento.

La memoria centrale dinamica ha elevata capacità ma è lenta. La CPU è costretta ad introdurre dei cicli di wait quando deve prelevare dati. La memoria cache invece è statica, quindi presenta un minor tempo di accesso. La memoria cache intercetta le richieste di accesso alla memoria centrale e provvede a mantenere una copia dei dati prelevati, in modo che in successive richieste possa fornirli riducendo gli accessi alla memoria dinamica.

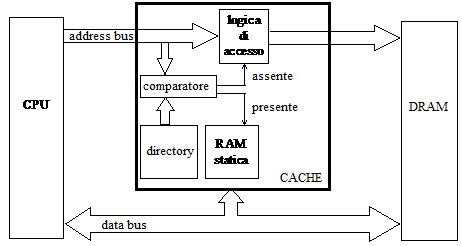

I dati letti dalla memoria centrale (DRAM) vengono immagazzinati nella cache insieme con l'informazione dell'indirizzo in cui sono memorizzati. La parte indirizzo viene scritta nella directory, e la parte valore viene scritta nella RAM statica

La CPU chiede l'accesso ai dati depositando sull'Address Bus l'indirizzo di memoria. La cache ha un comparatore per verificare rapidamente se l'indirizzo presente sul bus è già contenuto nella directory. Se il confronto d´ esito positivo, il dato è presente e la cache lo deposita sul data bus, se invece il confronto dé esito negativo allora l'indirizzo viene presentato alla memoria centrale per ottenere il valore cercato. In questo caso il dato viene prelevato dalla CPU, ma anche la cache se ne fa una copia in previsione di accessi futuri.

Tempo medio di accesso

La memoria cache permette alla CPU di funzionare senza cicli di attesa. La frazione di accessi positivi è misurata dal rapporto tra il numero di dati forniti direttamente dalla cache e il numero totale di riferimenti a dati in memoria:

f = (numero di successi) / (numero totale di accessi)

Una frazione di successi 0.9 significa che la memoria si comporta per il 90% dei casi come memoria statica e per il restante 10% come memoria dinamica. Se l'accesso alla cache dura 100 ns e l'accesso alla memoria centrale dura 300 ns, con una frazione di successi del 90%, il tempo medio di accesso è:

tm = 100 ns · 0.9 + 300 ns · 0.1 = 120 ns

(Principio della località) Per aumentare la frazione di successi non serve aumentare la dimensione della cache. La frazione di successi dipende dall'organizzazione dei programmi; questi sono formati principalmente da cicli di istruzioni che usano frequentemente gli stessi dati; vale a dire che, per la maggior parte del tempo, l'esecuzione dei programmi avviene su istruzioni e variabili a cui si era già effettuato l'accesso. In tal caso i dati e le istruzioni vengono prelevati solo al primo accesso, per tutti gli accessi successivi la CPU li trova già nella cache.

Sistemi multiprocessore

Nei sistemi in cui sono presenti più CPU, la memoria centrale è comune a tutte le CPU e, in un certo istante, l'accesso alla memoria centrale può essere concesso ad una sola di esse. Se però ogni CPU ha la propria cache allora si riducono i possibili conflitti nell'accesso simultaneo alla memoria.

Operazioni di aggiornamento dei dati

Finora la memoria cache è stata descritta per operazioni di sola lettura. Ma se la CPU modifica i dati sorgono dei problemi:

i dati nella cache sono diversi dai corrispondenti dati nella memoria centrale,

la CPU deve attendere che il dato venga scritto anche nella memoria centrale,

altre CPU devono essere informate che il dato nella memoria centrale non è ancora aggiornato.

Tecnica write through. Se la CPU modifica un dato nella cache, questo viene scritto immediatamente anche nella memoria centrale. È la tecnica che assicura la coerenza dei dati ma impegna la CPU ad aspettare il completamento dell'operazione.

Tecnica write later. La CPU scrive solo nella cache, poi un circuito cache controller si assicura che nessuna CPU prelevi il dato dalla memoria prima che questo venga aggiornato con il valore contenuto nella cache.

Tecnica buffered write through. La CPU scrive i dati sia nella cache che in un buffer, in modo che la CPU continua ad usare la cache mentre una circuiteria completamente indipendente provvede a copiare il dato dal buffer alla memoria centrale. Se prima che questa operazione di copia venga completata si ha una nuova operazione di aggiornamento dei dati nella cache, allora la CPU deve attendere che il buffer si svuoti. Comunque questo è un caso talmente raro da poter preferire la tecnica buffered write through rispetto alle altre due.

Snooping.

Nei sistemi con più CPU si deve assicurare che ogni CPU usi gli stessi valori per le variabili comuni. Cioè se una CPU-1 modifica un dato nella memoria centrale, e questo dato è usato da una CPU-2 che lo ha già disponibile nella sua cache, il cache controller deve riconoscere le operazioni di scrittura in memoria e deve provvedere a notificare alla cache della CPU-2 che il dato che possiede non è valido e deve essere aggiornato in un successivo riferimento. Questo meccanismo di controllo degli accessi alla memoria centrale è detto snooping. Il problema non riguarda solo i sistemi con più CPU, anche il DMA deve poter avere la possibilità di funzionare in parallelo alla CPU.

La directory della cache

La directory della cache è una tabella contenente gli indirizzi della memoria centrale il cui contenuto è presente nella RAM statica della cache. Per ogni accesso alla memoria centrale un comparatore controlla se l'indirizzo presente sull'address bus è contenuto nella directory.

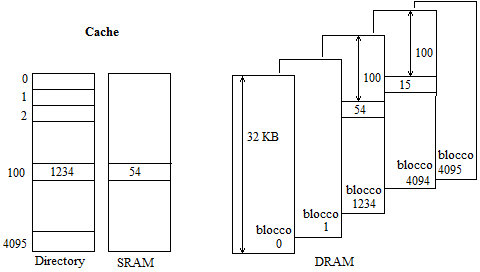

Si supponga che la capacità della memoria centrale sia = 227 = 128 MB, la capacità della SRAM della cache si 215 = 32 KB. Si considera che la memoria centrale sia suddivisa in blocchi da 32 KB, pari alla dimensione della SRAM, cioè il numero di blocci è: 227/215=212 = 4096.

Con i valori dell'esempio, risulta che servono 27 bit per indirizzare una locazione della memoria, di cui 12 individuano il numero del blocco e 15 individuano l'offset all'interno del blocco.

La figura mostra che l'indirizzo presente sull'address bus fa riferimento alla locazione che si trova all'offset 100 del blocco 1234. Il comparatore accede alla locazione all'offset 100 della directory della cache e verifica se il numero del blocco è uguale a 1234. Se il confronto d´ esito positivo la cache fornisce il valore (54) sul data bus, altrimenti aspetta che la memoria centrale lo fornisca per farsene una copia.

Successivamente, se la CPU accede alla locazione 100 del blocco 4095, il dato nella cache (54) viene sovrascritto con il nuovo valore (15).